|

|

|

| Главная Журналы Популярное Audi - почему их так назвали? Как появилась марка Bmw? Откуда появился Lexus? Достижения и устремления Mercedes-Benz Первые модели Chevrolet Электромобиль Nissan Leaf |

Главная » Журналы » Absorbing materialorganic polymer 1 ... 49 50 51 52 53 54 55 a negative gate voltage. Thus, an inversion Jayer of mobile charge сип be created adjacent to the oxide. The basic MOS field-effect action is the modulation of the inversion charge density, or channel conductance, by the gate voltage. The C- V characteristics of the MOS capacitor were considered. The amount of equivj oxide trapped charge and the density of interface states, for example, can be determii from the C-V measurements. Two basic types of MOSFFTs are the n channel, in which current is due to the flow of electrons in the inversion layer, and the p channel, in which current is due to the flow of holes in the inversion layer. Fach of these devices can be cither enhancement mode, in which the device is normally off and is turned on by applying a gate voltage, or depletion mode, in which the device is normally 4>n and is turned off by applying a gate voltage. The flat-band voltage is the gale voltage that must be applied to achieve the llat-band condition, in which the conduction and valence bands in the semiconductor do not ben and there is no space charge region in the semiconductor. The flat-band voltage is a function of the metal-oxide barrier height, the sem icond uctor-iixide hairier height, anc the amount of fixed trapped oxide charge. The threshold voltage is the applied gate voltage required to reach the threshold inversion point, which is the condition at which the inversion charge density is equal in magnitude to the semiconductor doping concentration. The threshold voltage is a function of the flat-band voltage, semiconductor doping concentration, and oxide thickness. The current in a MOSFFf is due to the flow of carriers m the inversion layer between the source and drain terminals. The inversion layer charge density and channel conductance are controlled by the gate voltage, which means that the channel currem is also controlled by the gate voltage. When the transistor is biased in the nonsaturation region {Vs < ViTsat)), the inversion charge extends completely across the channel from the source to the drain terminals. The drain current is a function of both the gate-to-source and drain-to-source voltages- When the transistor is biased in the saturation region (Vds > Vo.tsat)), the inversion charge density is pinched off near the drain terminal, and the ideal drain current is only a function of the gate-to-source voltage. The MOSFET is actually a four-terminal device, with the substrate or body being the fourth terminal. As the magnitude of the re verse-bias source-to-substrate voltage increases, the magnitude of the threshold voltage increases. The substrate bias effect may become important in integrated circuits in which the source and substrate are not electrically tied together , Asmail-signalequivalentcircuit,including capaci tances, of the MOS FET was developed The various physical factors in the MOSFET that affect the frequency limitations were considered. In particular, the drain overlap capacitance may be a limitmg factor in the frequency response of the MOSFET because of the Miller effect. The cutoff frequency, a figure of merit for the frequency response of the device, is inversely proportional to channel length: thus, a reduction in channel length results in an increased frequency \ capability of the MOSFET The CMOS technology, in which both n-channel and p-channel devices are fabricated in the same semiconductor chip, was briefly considered. Electrically isolated p- and n-substrate regions arc required to acconunodate the two types of transistors. Various processes are used to fabricate this structure. One potential problem encountered in the CMOS structure is latch-up-the high-cuiTcnt, low-voltage condition that may occur in a four-layer pnpn structure. Glossary of Important Terms 511 GLOSSARY OF IMPORTANT TERMS accumulation layer cliarge The induced charge directly under an oxide that is in excess of the thermal-equilibrium majority carrier concentration. bulk charge effect The deviation in drain current from the ideal due to the space charge width variation along the channel length caused by a drain-to-source vohage. channel conductance The ratio of drain current to drain-to-source voltage in the limit as channel conductance modulation The process whereby the channel conductance varies with gate-to-source voltage. CMOS Complementary MOS; the technology that uses both p- and n-channel devices in an electronic circuit fabricated in a single semiconductor chip. cutoff frequency The signal frequency at which the input ac gate current is equal to the output ac drain current. depletion mode MOSFET The type of MOSFET in which a gate voltage must be applied to turn the device off. enhancement mode MOSFET The type of MOSFET in which a gate voltage must be applied to turn the device on. equivalent fixed oxide charge The effective fixed charge in the oxide, g, directly adjacent to the oxide-semiconductor interface. flat-hand voltage The gate voltage that must be applied to create the flat-band condifion in which there is no space charge region in the semiconductor under the oxide, gate capacitance charging time The time during which the input gale capacitance is being charged or discharged because of a step change in the gate signal. interface states The allowed electronic energy states within the bandgap energy at the oxi de-sem iconductor in terface. inversion layer charge The induced charge direcdy under the oxide, which is the opposite type compared with the semiconductor doping. inversion layer mobility The mobility of carriers in the inversion layer latch-up The high-current, low-voltage condifion that may occur in a four-layer pnpn structure such as in CMOS. maximum induced space charge width The width of the induced space charge region under the oxide at the threshold inversion condition. metal-semiconductor work function difference The parameter ф, < a function of the difference between the inetal work function and semiconductor electron affinity. moderate inversion The condition in which the induced space charge width is changing shghtly when the gate voltage is at or near the threshold voltage and the inversion charge density is of the same magnitude as the semiconductor doping concentrafion. oxide capacitance The ratio of oxide permitfivity to oxide thickness, which is the capacitance per unit area, Со?. saturation The condition in which the inversion charge density is zero at the drain and the drain current is no longer a function of the drain-to-source voltage. strong inversion The condition in which the inversion charge density is larger than the magnitude of the semiconductor doping concentration, threshold inversion point The condition in which the inversion charge density is equal in magnitude to the semiconductor doping concentration. threshold voltage The gate voltage that must be applied to achieve the threshold in vers point. transconductance The ratio of an incremental change in drain current to the correspondiij incremental change in gate voltage, - weak inversion The condition in which the inversion charge density is less than the tude of the semiconductor doping concentradon. CHECKPOINT After studying this chapter, the reader should have the ability to: Sketch the energy band diagrams in the semiconductor of the MOS capacitor under various bias conditions. Describe the process by which an inversion layer of charge is created in an MOS capacitor. Discuss the reason the space charge width reaches a maximum value once the inversion layer is formed. Discuss what is meant by the metal-semiconductor work function difference, and discuss why this value is different between aluminum, n polysilicon, and p polysilicon gates. Describe what is meant by flat-band voltage. Define threshold voltage. Sketch the C-V characteristics of an MOS capacitor with p-type and n-type semiconductor substrates under high-frequency and low-frequency conditions. DLscuss the effects of fixed trapped oxide charge and interface states on the C-V characteristics. Sketch the cross-sections of n-channel and p-channel MOSFET structures. Explain the basic operation of the MOSFET. Discuss the I-V characteristics of the MOSFET when biased in the nonsaturation and saturation regions. Describe the substrate bias effects on the threshold voltage. Sketch the small-signal equivalent circuit, including capacitances, of the MOSFET, and explain the physical origin of each capacitance. Discuss the condition that defines the cutoff frequency of a MOSFET. Sketch the cross section of a CMOS structure. Discuss what is meant by latch-up in a CMOS structure. REVIEW QUESTIONS 1. Sketch the energy band diagrams in an MOS capacitor with an n-type substrate in accumulation, depletion, and inversion modes, 2. Describe what is meant by an inversion layer of charge. Describe how an inversion layer of charge can be formed in an MOS capacitor with a p-type substrate. 3. Why does the space-charge region in the semiconductor of an MOS capacitor reach a maximum width once the inversion layer is formed? 4. Define electron affinity in the semiconductor of an MOS capacitor. 5. Sketch the energy band diagram through an MOS structure with a p-iype substrate and an n polysilicon gate under zero bias. Problems S13 6. Define the flat-band voltage. 7. Define the threshold voUage. H, Sketch the C-V characterisfics of an MOS capacitor with an n-type substrate under the low-frequency condition. How do the characterisfics change for the high-frequency condifion? 9. Indicate the approximate capacitance at flat-band on the C-V characteristic of an MOS capacitor with a p-type substrate under the high-frequency condifion. 10. What is the effect on the C-V characteristics of an MOS capacitor with a p-type substrate if the amount of posifive trapped oxide charge increases? 11. Quafitafively sketch the inversion charge density in the channel region when the transistor is biased in the nonsaturation region. Repeal for the case when the transistor is biased in the saturation region. 12. Define V;,.v(sat). 13. Define enhancement mode and depletion mode for both ii-channel and p-channel devices. 14. Sketch the charge distribution through an MOS capacitor with a p-type substrate when biased in the inversion mode. Write the charge neutrality equafion. 15. Discuss why the threshold voltage changes when a reverse-biased source-to-substrate voltage is applied to a MOSFET PROBLEMS {Note: In the following problems, assume the semiconductor and oxide in the MOS system are silicon and silicon dioxide, respectively, and assume the temperature is T 300 К unless otherwise stated. Use Figure 11.15 to determine the metal-semiconductor work function difference.) Section 11Л The Two-Terminal MOS Structure Jl.l The dc charge distributions of four ideal MOS capacitors are shown in Figure 11.62. For each case: (a) Is the semiconductor n- or p-type? (h) Is the device biased in the accumulation, depletion, or inversion mode? (c) Draw the energy-band diagram in the semiconductor region. 11.2 (a) Calculate the maximum space charge width .r/ г and the maximum space charge density Q.jr,(max)[ in p-type silicon, gaUium arsenide, and germanium semiconductors of an MOS structure. Let Г = 300 К and assume N - 10 cin \ (h) Repeat part (a) if r 200 K. IL3 {a} Consider n-type sihcon in an MOS structure. Let f ~ 300 K. Determine the semiconductor doping so that IQjCmax)] ==7.5 x 10 Clcrn. (b) Determine the suriace potential that results in the maximum space charge width. 1L4 Detennine the metal-semiconductor work function difference ф, in an MOS structure with p-type sificon for the case when the gate is (a) aluminum, (/?) n+ polysilicon, and (c) p+ polysilicon. Let iVj 6 x lO- cm~-. П.5 Consider an MOS structure with n-type silicon. A metal-semiconductor work function difference of < -0.35 V is required. Determine the silicon doping required to meet this specification when the gate is (a) n polysilicon, (b) polysilicon, and (c) aluminum. If a particular gate cannot meet this requirement, explain why. О

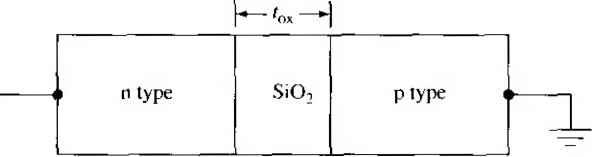

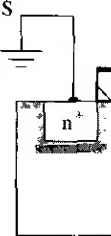

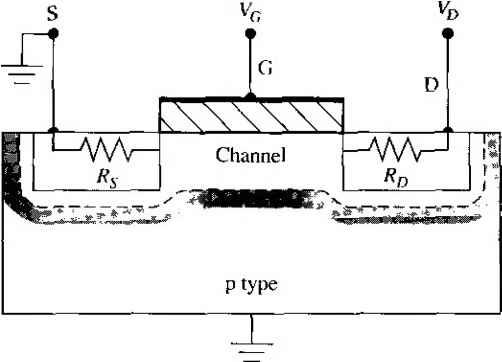

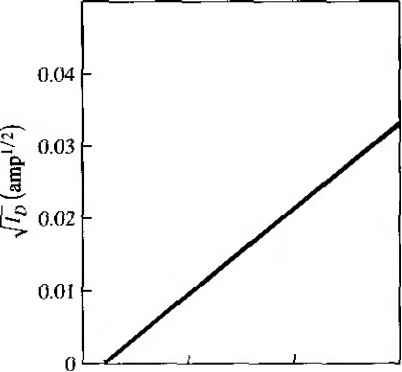

О Figure 1L62 I Figure for Problem 11Л 11.6 11.8 11.9 11.10 Consider an polysilicon-silicon dioxide-n-type silicon MOS capacitor. Let iVj = 10 cm~. Calculate the flat-band voltage for (a) fox = 500 A when Q] is 0) 10 cm- iii) 101 cm-% and (ш) 5 x lOi cm . Repeat part (a) when t, = 250 A. 11.7 Consider an aluminum gate-silicon dioxide-p-type silicon MOS structure with = 450 A. The silicon doping is N 2 x 10 cm and the flat-band voltage is VfTs = - LO V. Determine the fixed oxide charge . An MOS transistor is fabricated on a p-type silicon substrate with = 2 x 10 cm~. The oxide thickness is Гох = 450 A and the equivalent fixed oxide charge is = 2 x 10 cm. Calculate the threshold voltage for (a) an aluminum gate, (b) an n polysilicon gate, and (c) a p+ polysilicon gate. Repeat Problem 11.8 for an n-type sihcon substrate with Nd = 10** cm-. A 400 A oxide is grown on p-type silicon with =5 x 10 cm~\ The flat-band voltage is -0.9 V. Calculate the surface potential at the threshold inversion point as well as the threshold voltage assuming negligible oxide charge. Also find the maximum space charge width for this device. *11.11 An MOS transistor with an aluminum gate is fabricated on a p-type silicon substrate. The oxide thickness is fx = 750 A, and the equivalent fixed oxide charge is = 10 cm~. The measured threshold voltage is Vr = -h0.80 V. Determine the p-type doping concentration. Problems 515 *11.23 Using the results of Problem 11.22, calculate the shift in the flat-band voltage for the following oxide charge distributions: (a) Q = 5 x 10 cm~- is entirely  * 11.12 Repeat Problem 11.11 for an n-type silicon substrate if the measured threshold voltage is Vt - - 1.50 V. Determine the n-type doping concentration. 11.13 An Al-silicon dioxide-silicon MOS capacitor has an oxide thickness of 450 A and a doping of Na = 10 cm~. The oxide charge density is = 3 x 10 cm. Calculate (a) the flat-hand voltage and (h) the threshold voUage. Sketch the electric field through the structure at the onset of inversion. 11Л4 An n-channel depletion mode MOSFET with an n+ polysilicon gate is shown in Figure 11.42. The n-channel doping is N 10 cm *, and the oxide thickness is t = 500 A. The equivalent fixed oxide charge is = 10 cm~. The n-channel thickness is equal to the maximum induced space charge width. (Disregard the space charge region at the n-channel-p-substrate juncfion.) (a) Determine the channel thickness , and (b) calculate the threshold voltage. 11.15 Consider an MOS capacitor with an n polysilicon gate and n-type silicon substrate. Assume Na = 10 cm and let £/r - E. = 0.2 eV in the n+ polysilicon. Assume the oxide has a thickness of f = 300 A. Also assume that (polysilicon) = у/ (single-crystal silicon), (a) Sketch the energy-band diagrams {/) for Vc =0 and (n) at flat band, (h) Calculate the metal-semiconductor work function difference. (c) Calculate the threshold voltage for the ideal case of zero fixed oxide charge and zero interface states. 11.16 The threshold voltage of an n-channel MOSFET is given by Equation (11.27). Plot Vf versus temperature over the range 200 5 T < 450 K. Consider both an alu-rninum gate and an n polysihcon gate. Assume the work funcfions are independent of temperature and use device parameters similar to those in Example 11.4. 11.17 Plot the threshold voltage of an n-channel MOSFET versus p-type substrate doping concentration similar to Figure 11.20. Consider both n and p polysilicon gates. Use reasonable device parameters. 11.18 Plot the threshold voltage of a p-channel MOSFET versus n-type substrate doping concentration similar to Figure 11.21. Consider both n and p polysihcon gates. Use reasonable device parameters. 11Л9 Consider an NMOS device with the parameters given in Problem 11.10. Plot Vf versus ox over the range 20 < fx < 500 A. -LJJ Section 11.2 Capacitance-Voltage Characteristics 11.20 An ideal MOS capacitor with an aluminum gate has a silicon dioxide thickness of = 4(X) A on a p-type silicon substrate doped with an acceptor concentration of Na 10 cm~-\ Determine the capacitances C, CJj, CJ, and C4inv) at (й) / 1 Hz and (h) f = 1 MHz. (c) Determine VfB and Vf. Sketch C/C, versus Vg for parts {a) and (b). 11.21 Repeat Problem 11.20 for an n-type silicon substrate doped with a donor concentration of jV,/ = 5 x 10 cm-\ *11.22 Using superposition, show that the shift in the flat-band vohage due to a fixed charge distribution p{x) in the oxide is given by 1 .VP(л) AVfb = -r- / --dx  11.27  located at the oxide-semiconductor interface. Let = 750 A. {h) Q[ = 5 X 10 cm~ is uniformly distributed throughout the oxide, which has a thi of 750 A. (c) Q =5 X 10 cm~- forms a triangular distribution with the peak -dtx - /ox - 750 A (the oxide-semiconductor interface) and which goes to zero at jc = 0 (the metal-oxide interface). 11.24 An ideal MOS capacitor is fabricated by using intrinsic silicon and an n+ polysilico gate, (a) Sketch the energy-band diagram through the MOS structure under flat-ban conditions, ф) Sketch the low-frequency C-V characteristics from negative to positive gate voltage. 11.25 Consider an MOS capacitor with a p-type substrate. Assume that donor-type interface traps exist only at midgap (i.e., at Я^/)- Sketch the high-frequency C-V curve from accumulation to inversion. Compare this sketch to the ideal C-V plot. 11.26 Consider an SOS capacitor as .shown in Figure 11.63. Assume the Si02 is ideal (no trapped charge) and has a thickness of tax = 500 A. The doping concentrations are = {Q cm and Na 10 cm~, (a) Sketch the energy band diagram through the device for (/) flat-band, ( ) Vc +3 V, and (iii) Vo = -3 V. (b) Calculate the flat-band voltage, (c) Estimate the voltage across the oxide for (i) Va = +3 V and ( ) Vo = - 3 V. () Sketch the high-frequency C-V characteristic curve. The high-frequency C-V characteristic curve of an MOS capacitor is shown in Figure 11.64. The area of the device is 2 x 10 cm-. The metal-semiconductor work function difference is 0;., - -0.50 V, the oxide is Si02, the semiconductor is silicon, and the semiconductor doping concentration is 2 x 10 cm(a) Is the  Figure 11.63 1 Figure for Problem 11.26.

-O.RV Figure 1L64 I Figure for Problem 11.27. Problems С  О Figure 11.65 I Figure for Problem 11.28. semiconductor n or p type? (h) What is the oxide thickness? (c) What is the equivalent trapped oxide charge density? (d) Determine the flat-band capacitance. 11.28 Consider the high-frequency C-V plot shown in Figure 11.65. (a) Indicate which points correspond to flat-band, inversion, accumuladon, threshold, and depletion mode, (b) Sketch the energy band diagram in the semiconductor for each condition. Section из The Basic MOSFET Operation 11.29 An expression that includes the inversion charge density was given by Equation (11.55). Consider the definition of threshold voltage and show that the inversion charge density goes to zero at the drain terminal at saturation. (Hint: Let - Vs = VDs(sat).) 11.30 An ideal n-channel MOSFET has the following parameters: W = 30 fim tin = 450 cmVV-s L = 2 jLim t = 350 A V =-h0.80V (fl) Plot Id versus V- for 0 < Vs < 5 V and for Vqs = 0. L 2, 3,4, and 5 V. Indicate on each curve the Vpsisixt) point, (b) Plot v77>Tsat) versus Vcs for 0 < Vc5 < 5 V. (c) Plot I о versus Vos for Yds = 0.1 V and for 0 < Vg5 S 5 V. 11.31 An ideal p-channel MOSFET has the following parameters: W = 15 дт 300 cm/V-s I = 1.5 дт Гох -- 350 A Yt = -0.80 V (a) Plot I о versus Vsd for 0 < Vd 5 5 V and for Ysa = 0, 1, 2, 3,4, and 5 V. Indicate on each curve the Vj:zj(sat) point, (h) Plot I о versus Ysg for Ysd =0A V and for 0 < VsG < 5 V. 11.32 Consider an n-channel MOSFET with the same parameters as given in Problem 11.30 except that Yj = -2.0 V. (a) Plot I о versus V. for 0 < Vd5 < 5 V and for Yes = -2, -1, 0, +1, and -Ь2 V. ф) Plot vTsat) versus Vcs for -2 < Vqs < +3 V.   ptype Figure 11,66 I Figure for Problem 11.33-  Figure 11.67 I Figure for Problem 1L34. 11.33 Consider an n-channel enhancement mode MOSFET biased as shown in Figure i 1.66, Sketch the current-voltage characteristics, > versus Vf}s> for {a) Vod = 0, (h) У^р = VrAand(c) VcD =2Vr. 11.34 Figure 11.67 shows the cross section of an NMOS device that includes source and , drain resistances. These resistances take into account the bulk n semiconductor resistance and the ohmic contact resistance. The current-voltage reladons can be generated by replacing Vcs by Vc - Ins and Vos by VJ - lois + Rp) in the ideal equations. Assume transistor parameters of VV = 1 V and AT - 1 mA/V. (a) Plot the following curves on the same graph: Ip versus Vp for Vc 2 V and Vc = 3 V over the range 0 < < 5 V for (0 = RjO and {ii) Rs Rd 1 kfi. (b) Plot the following cur\es on the same graph: /l versus Vc for Vp =ОЛУ and Vp=5V over the range 0 < < 1 niA for (/) Rs = RpQ and (/7) Rs Rp = \ 11.35 An n-channel MOSFET has the same parameters as given in Problem 11.30. The gate terminal is connected to the drain terminal. Plot Ip versus Vp for 0 < Vns- < 5 V. Determine the range of Vps over which the transistor is biased in the nonsaturation and saturaiion regions. Problems 0.05  Vgs (volts) Figure 11.68 I Figure for Problem 11.37. 11.36 The channel conductance for a p-channel MOSFET is defined as dVsD Plot the channel conductance for the p-channel MOSFET in Problem 11.31 for 0 < 5 5 V. 11.37 The experimental characterisfics of an ideal л-channel MOSFET biased in the saturation region are shown in Figure 11.68. If W/L =10 and = 425 A, determine Vj and д„. 11.38 One curve of an n-channel MOSFET is characterized by the following parameters: /D(sat) = 2 X 10- A, Vo5(sat) = 4 V, and Vr = 0.8 V. {a) What is the gate voltage? (b) What is the value of the conduction parameter? (c) If Vc = 2 V atid Vos = 2 V, determine io -{d) If Vg 3 V and V = 1 V, determine I о (e) For each of the conditions given in (c) and {d), sketch the inversion charge density and depletion region through the channel. 11.39 (a) An ideal n-channel MOSFET has an inversion carrier mobility д„ = 525 cm/V-s, a threshold voltage Vt = +0.75 V, and an oxide thickness tx = 400 A. When biased in the saturation region, the required rated current is /о(а1) = 6 mA when Vas 5 V. Determine the required W/L rafio. (/?) A p-channel MOSFET has the same requirements when Vcs = 5 V and has the same parameters as part {a) except fip = 300 cm/V-s and Vt = -0.75 V. Determine the W/L rafio. 11.40 Consider the transistor described in Problem 11.30. (я) Calculate g,fti for Vos =0.5 V. Calculate g Лог Va5 = 4 V. 11.41 Consider the Uransistor described in Problem 11.31. (я) Calculate g , l for Vd = 0.5 V. (b) Calculate g s for Vsc = 4 V. 1 ... 49 50 51 52 53 54 55 |

|||||||||||||||||||||

|

© 2026 AutoElektrix.ru

Частичное копирование материалов разрешено при условии активной ссылки |